想象一下,在一场精密的双人芭蕾中,两位舞者必须保持完美的同步与平衡——这正如高频电路中的差分对信号。在高速数据传输的舞台上,这对“电子舞者”的配合默契程度,直接决定了整个系统的表现。

差分对的本质

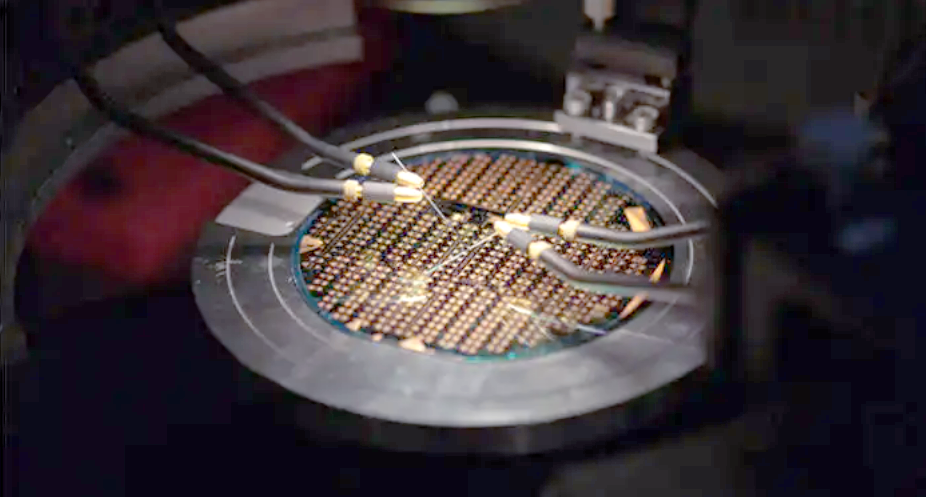

差分对由两条紧密耦合的传输线组成,它们承载着幅度相等、相位相反的信号。这种设计不仅提高了抗干扰能力,更成为了高速数字电路(如USB、HDMI、PCI Express)和射频电路的核心传输方式。但要让这对“舞伴”在高频环境下完美配合,阻抗匹配便是关键所在。

阻抗匹配的核心技巧

1.严格保持差分对长度、宽度及间距的对称性,长度偏差通常需小于0.127毫米。

2.恒定控制线间距,约为线宽的1.5-2倍,转弯时使用圆弧。

3.确保下方有完整无分割的地平面作为参考,换层时增加接地过孔。

4.根据频率、功耗和拓扑精心选择端接方案(如并联电阻)。

5.高频应用优先选用低损耗、介电稳定的板材(如罗杰斯系列),以减少信号衰减。

高多层PCB的防静电,绝非在某一环节增加一个器件那么简单。它是一个从设计源头发起,贯穿材料选择、PCB制造、直至SMT贴装完成的系统性防护工程。唯有在每个环节都建立严密的“绝缘-泄放-屏蔽”体系,才能构建起对抗这位“隐形刺客”的铜墙铁壁,保障高密度、高性能电子设备的核心载体安然无恙。

我是工艺部张经理,深耕PCB工艺十年,经手过上千款高多层PCB的工艺优化,见过太多因防静电不到位导致的损耗。