12月24日消息,半导体大厂英特尔(Intel)近日展示了其在先进封装领域的最新研发成果,推出一系列以Intel 18A 与Intel 14A 等先进节点制程的多芯粒(Multi-chiplet)产品概念。不仅展现了英特尔在Foveros 3D 与EMIB-T 先进封装技术上的突破,更传递出其希望在高性能计算(HPC)、人工智能(AI)及数据中心市场与台积电的CoWoS 封装技术一决高下的信心。

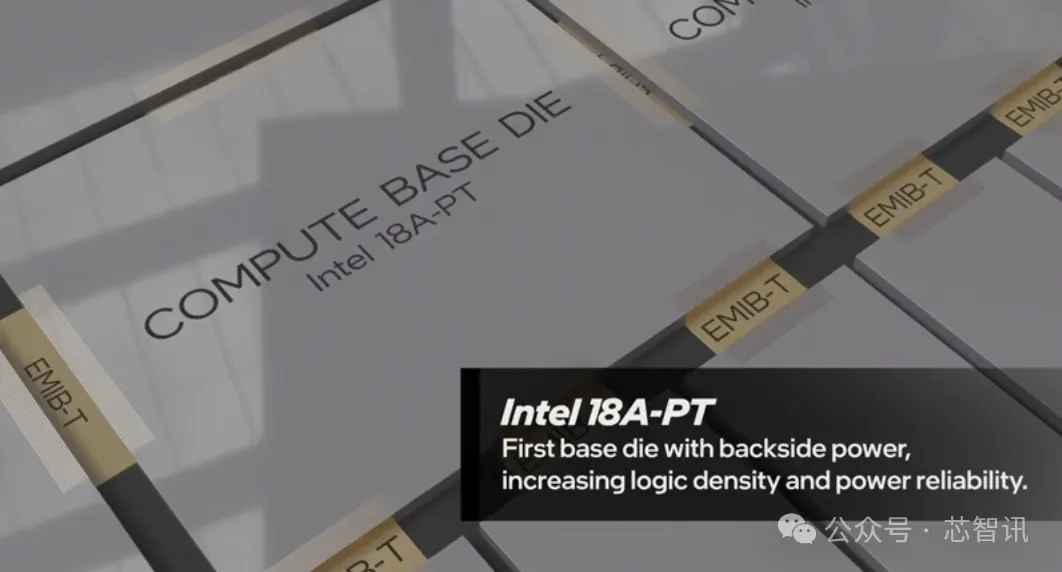

英特尔本次技术展示的核心在于其精密且具高度扩展性的先进封装构架。根据数据显示,英特尔将利用Intel 14A-E 节点制程提供突破性的逻辑性能,该制程同时采用了第二代RibbonFET晶体管与全新的PowerDirect 技术。而在基础芯片部分,则采用Intel 18A-PT 制程,这是首款采用背面供电技术的基础芯片,能显著提升逻辑密度与电力供应的可靠性。

此外,为了达到极致的垂直堆叠目标,英特尔还导入了Foveros Direct 3D 技术,通过极细间距的混合键合(Hybrid Bonding)进行精密3D 堆叠。而在多芯粒互连方面,新一代的嵌入式多芯片互连桥接(EMIB-T)技术加入了硅穿孔(TSV)技术,可提供更高的带宽,并整合更大规模的晶片组。

另外,英特尔还在展示视频中披露了两款极具前瞻性的概念设计,展现了其超越传统光罩限制(Reticle Limit)的技术实力。其中在中阶解决方案方面,可配备4个计算芯片与12个HBM。至于在旗舰解决方案方面,则是将规模扩大到16个计算芯片与24个HBM ,并可配置多达48个LPDDR5X 控制器,极大化AI 与数据中心工作执行所需的内存密度。

而且,这些设计采用了类似“Clearwater Forest”的构架,其基础芯片负责搭载SRAM,并通过Foveros 3D 技术将顶层包含AI 引擎或CPU IP的计算芯片堆叠在上面。内存支持方面,英特尔强调其封装方案能无缝兼容目前的HBM3/HBM3E,以及未来的HBM4、HBM5 等新一代标准。

编辑:芯智讯-林子